## 2038

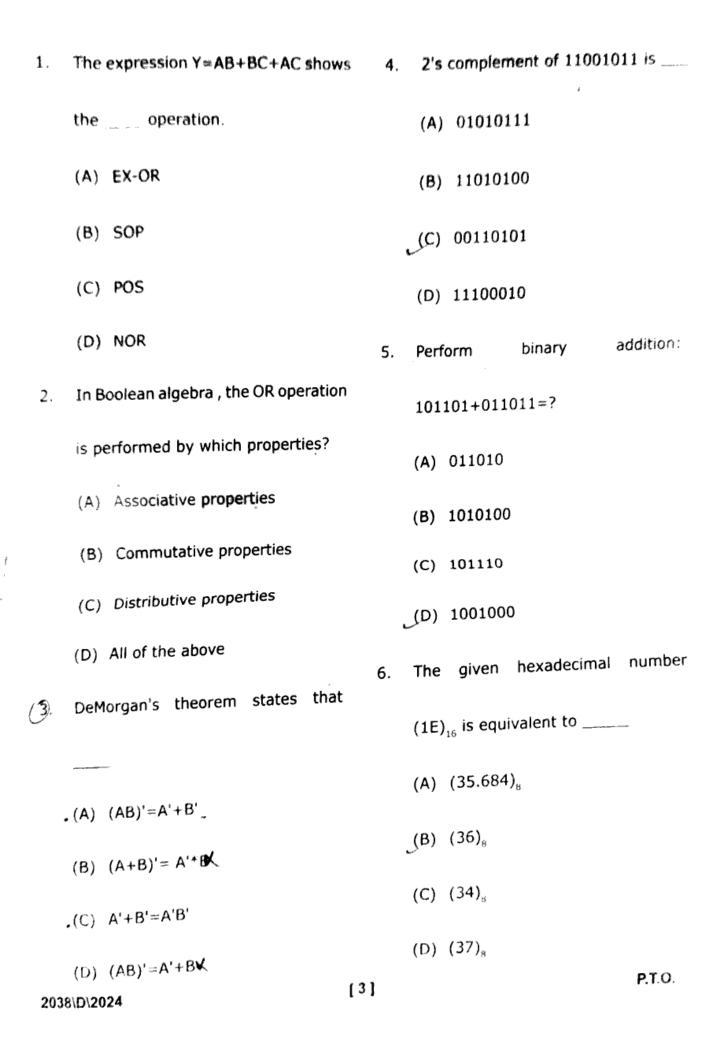

# B.C.A. (H Sem.) Examination, 2023-24

**Booklet Series**

D

#### DIGITAL ELECTRONICS

(To be filled by the Candidate / निम्न पूर्तियाँ परीक्षार्थी स्वयं भरें)

Roll No. (in figures).

अनुक्रमांक (अंकों में) --

Roll No. (in words) अनुक्रमांक (शब्दों में) —

Name of Examination Centre, परीक्षा केन्द्र का नाम | Time : 2 : 00 Hours | समय : 2 : 00 घण्टे

| Maximum Marks : 50

[ **अधिक**तम अंक : 50

Signature of Invigilator कक्ष निरीक्षक के हस्ताक्षर

#### Instructions to the Examinee:

- Do not open the booklet unless you are asked to do so.

- The booklet contains 75 questions. Examinee is required to answer any 65 questions in the OMR Answer-Sheet provided and not in the question booklet. In case Examinee attempts more than 65 Questions, first 65 attempted questions will be evaluated. All questions carry equal marks.

- Examine the Booklet and the OMR Answer-Sheet very carefully before you proceed. Faulty question booklet due to missing or duplicate pages/questions or having any other discrepancy should be immediately replaced.

(Remaining Instructions on last page)

### परीक्षार्थियों के लिए निर्देश :

- प्रश्न-पुस्तिका को तब तक न खोतें जब तक आपसे कहा न जाए।

- 2. प्रश्न-पुस्तिका में 75 प्रश्न हैं। परीक्षार्थी को किन्हीं 65 प्रश्नों को दी गई ओ०एम०आर० आन्सर-शीट पर ही हल करना है। परीक्षार्थी द्वारा 65 से अधिक प्रश्नों को हल करने की स्थिति में, प्रथम 65 उत्तरों को ही मूल्यांकित किया जायेगा। सभी प्रश्नों के अंक समान हैं।

- उ. प्रश्नों के उत्तर अंकित करने से पूर्व प्रश्न-पुस्तिका तथा OMR उत्तर-पत्रक को सावधानीपूर्वक देख लें। दोषपूर्ण प्रश्न-पुस्तिका, जिसमें कुछ भाग छपने से छूट गये हों या प्रश्न एक से अधिक बार छप गये हों या किसी भी प्रकार की कमी हो, उसे तुरन्त बदल लें।

(शेष निर्देश अन्तिम पृष्ठ पर)

| 13. The full form of SIPO is        | 16. How is a J-K flip-flop made to toggle?       |

|-------------------------------------|--------------------------------------------------|

| (A) Serial-in Parallel-out          | (A) J=0, K=0                                     |

| (B) Serial-in Parity-out            | (B) J=1, K=0<br>(C) J=0, K=1                     |

| (C) Serial-In Peripheral-Out        | (D) J=1, K=1                                     |

| (D) None of above                   | 17. Which error detection method                 |

| 14. In D register, 'D' stands for   | consists of just one redundant bit               |

| (A) Delay                           | per data unit?                                   |

|                                     | (A) Simple parity check                          |

| (B) Decrement                       | (B) Two-dimensional parity check                 |

| _(C) Data                           | (C) CRC                                          |

| (D) Decay                           | (D) Checksum  (18. If we record any music in any |

| 15. Ripple counters are also called | recorder, such types of process is               |

| (A) SSI counters                    | called                                           |

| (B) Asynchronous counters           | _(A) Multiplexing                                |

| (C) Synchronous counters            | <b>★</b> (B) Encoding                            |

| (D) VLSI counters                   | (C) Plexing  (D) Demultiplexing                  |

| 2038\D\2024                         | [5] P.T.O.                                       |

| 19 The decimal equivalent of the binar              | y 22 A demultiplexer has :               |

|-----------------------------------------------------|------------------------------------------|

| number (1011), is                                   | (A) One data input and a number of       |

| (A) (10.123) <sub>10</sub>                          | selection inputs and they have           |

| (B) (14.175) <sub>10</sub>                          | several outputs                          |

| ( , , , , , , , , , , , , , , , , , , ,             | (B) One input and one output             |

| (C) (9.23) <sub>10</sub>                            | (C) Several inputs and several           |

| (D) (11) <sub>10</sub>                              | outputs                                  |

| 20. The representation of octal (5) <sub>8</sub> in | (D) Several inputs and one output        |

| decimal is equal to?                                | 23. In boolean algebra, the OR operation |

| (A) 15                                              | is performed by which properties?        |

| (A) 13                                              | (A) Associative properties               |

| (B) 55                                              | (B) Commutative properties               |

| JC) 5                                               | (C) Distributive properties              |

| (D) None of above                                   | (D) All of the above                     |

| •                                                   | 24. In the decimal numbering system.     |

| 21. The representation of octal number              | What is the MSD?                         |

| (532) <sub>8</sub> in decimal is                    | (A) The middle digit of a stream of      |

| (A) (346) <sub>10</sub>                             | numbers                                  |

| (B) (532) <sub>10</sub>                             | $t^{(B)}$ The digit to the right of the  |

| (5) (552)10                                         | decimal point                            |

| (C) (340) <sub>10</sub>                             | (C) The last digit on the right          |

| (D) (531) <sub>10</sub>                             | (D) The most significant digit           |

| 2038\D\2024                                         | [6]                                      |

|                                                     |                                          |

https://www.rmpssuonline.com

| 25.  | The full form of SR is:             | 29. A st | nift register is defined as :     |

|------|-------------------------------------|----------|-----------------------------------|

|      | (A) System Rated                    | (A)      | The register capable of shifting  |

|      | (B) Set Reset                       |          | information to another register   |

| 26.  | (C) Set Ready                       | (B)      | The register capable of shifting  |

|      | (D) Set Rated                       |          | information either to the right   |

|      | The complement of a variable is     |          | or to the left                    |

|      | always :                            | (C)      | The register capable of shifting  |

|      | (A) 0                               | (0)      | •                                 |

|      | (B) 1                               |          | information to the right only     |

|      | (C) Equal to the variable           | (D)      | None of these                     |

|      | (D) The inverse of the variable     | 30. The  | group of flip-flops is also known |

| 27.  | Which of the following is not a     | as:      |                                   |

|      | combinational circuit :             | _(A)     | Registers                         |

|      | (A) Adder                           | (B)      | Counters                          |

|      | (B) Code Converter                  | (C)      | Encoders                          |

|      | (C) Multiplexer                     | (D)      | None of the above                 |

|      | (D) Counter                         | 31. Sto  | rage of 1 KB means the following  |

| (28) | Which of the following flip-flop is | 1.       |                                   |

| •    | used by the ring counter?           | nun      | nber of bytes :                   |

| *    | (A) d flip-flop                     | (A)      | 1000                              |

|      | (B) SR flip-flop                    | (B)      | 964                               |

|      | (C) JK flip-flop                    | _(C)     | 1024                              |

|      | (D) T flip-flop                     | (D)      | 1064                              |

| 203  | 18\D\2024                           | [7]      | P.T.O.                            |

| ys.         | A flip-flop has                    | 41. Comparators are used in :                                    |      |

|-------------|------------------------------------|------------------------------------------------------------------|------|

|             | (A) One stable state               | (A) Cache devices (B) CPU                                        |      |

| •           | (B) No stable state                | (C) Motherboard                                                  |      |

|             | (C) Two stable state               | (D) Hard Drive                                                   |      |

|             | (D) None of the above              | 42. In Boolean algebra, the bar sign                             | (-)  |

|             | BCD counter is also known as :     | (A) OR operation                                                 |      |

|             | (A) Parallel Counter               | (B) AND operation                                                |      |

|             | (B) Decade Counter                 | (D) None of the above                                            |      |

|             | (C) Synchronous Counter            | 43. A shift register is defined as                               |      |

|             | (D) VLSI Counter                   | (A) The register capable of shifti information to another regist |      |

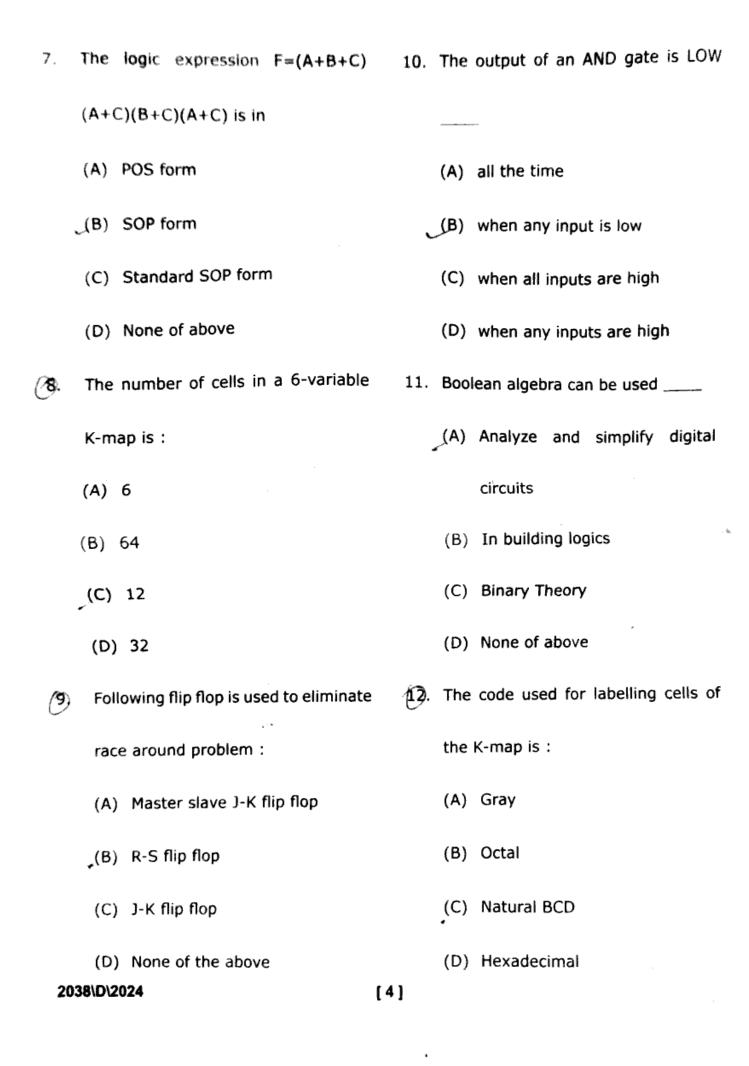

| <b>49</b> . | How many types of flip-flops are : | (B) The register capable of shift                                | ing  |

|             | (A) 2                              | or to the left                                                   | ąht  |

|             | (B) 3                              | (C) The register capable of shift                                | ing  |

|             |                                    | information to the right only                                    |      |

| ,           | ,(C) 4                             | (D) The register capable of shift information to the left only   | .ing |

| 203         | (D) 6<br>8\D\2024                  | [9] P.T.                                                         | .0.  |

| 44  | ADfl   | lip-flop can be        | constructe | d from  | 47.  | The  | decimal      | equivalent       | of    | the  |

|-----|--------|------------------------|------------|---------|------|------|--------------|------------------|-------|------|

|     | an     | flip-flop.             |            |         |      | exce | ss-3 numb    | er 11001010      | 0001  | 1 is |

|     | (A)    | S·R                    |            |         |      | (A)  | 970          |                  |       |      |

|     | (B)    | )-K                    |            |         |      | (B)  | 1253         |                  |       |      |

|     | (C)    | T                      |            |         |      |      |              |                  |       |      |

|     | (D)    | S-K                    |            |         |      | (C)  | 861          |                  |       |      |

| 45. | A K    | arnaugh map            | (K-map)    | is an   |      | (D)  | 1132         |                  |       |      |

|     | absti  | ract form of           | f d        | iagram  | 48.  | Whic | ch of the fo | ollowing is a v  | veigt | nted |

|     |        | nized as a ma          | •          | res.    |      | code | <b>:</b> ? . |                  |       |      |

|     | (A)    | Venn Diagram           | l          |         |      | (A)  | Gray-code    | 2                |       |      |

|     | (B)    | Cycle Di <b>agra</b> m | า          |         |      | ( )  | <b>,</b>     | _                |       |      |

| •   | (C)    | Block Diagran          | n          |         |      | (B)  | Excess-3     |                  |       |      |

|     | (D)    | Triangular Dia         | igram      |         |      | (C)  | Decimal N    | <b>lot</b> ation |       |      |

| 46. | Wha    | t is a Circuit?        |            |         |      | (D)  | None of the  | nese             |       |      |

|     | _(A)   | Open-loop th           | rough whic | h elec- | 49.  | The  | involution   | of A is equal    | to _  |      |

|     |        | trons can pas          | ss         |         |      | (A)  | A'           |                  |       |      |

|     | (B)    | Closed-loop            | through    | which   | 1    | (B)  | A            |                  |       |      |

|     |        | electrons can          | pass       |         |      |      |              |                  |       |      |

|     | (C)    | Both (A) and           | (B)        |         |      | (C)  | 0            |                  |       |      |

|     | (D)    | None of the r          | mentioned  |         |      | (D)  | 1            |                  |       |      |

| 203 | 8\D\20 | 24                     |            |         | [10] |      |              |                  |       |      |

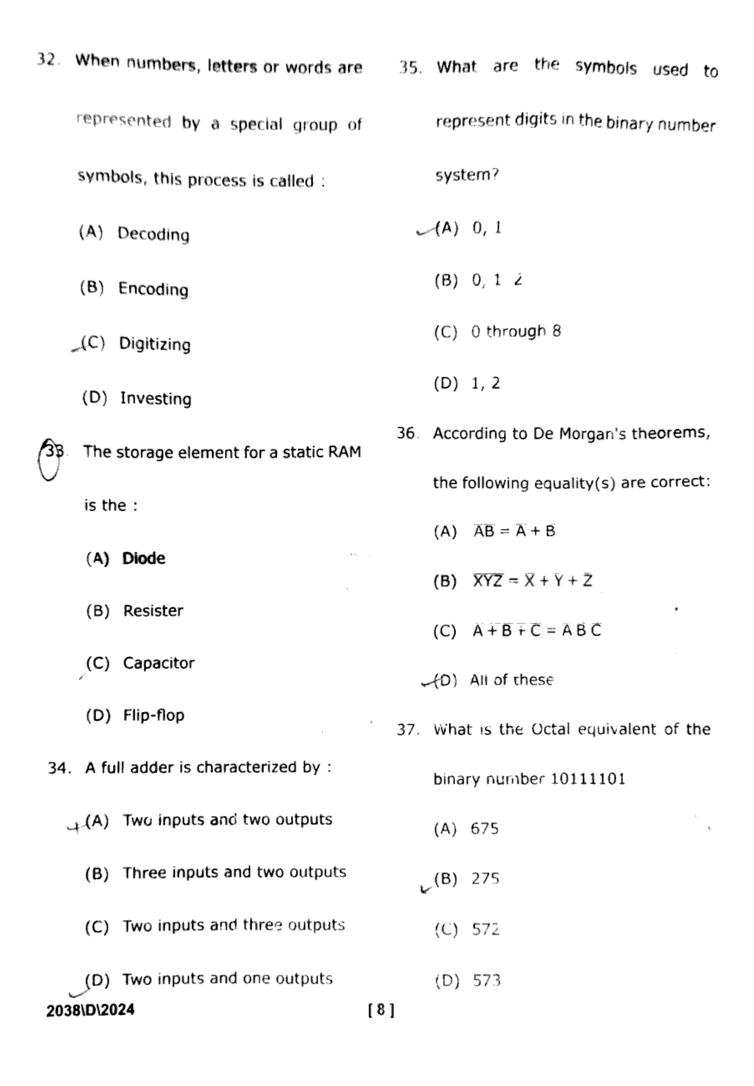

| 2038\D\20  | 24 [1                                                    | 1 ]         |       | P.T.O.                            |

|------------|----------------------------------------------------------|-------------|-------|-----------------------------------|

| c(0)       | All of the Mentioned                                     |             | (D)   | POS                               |

|            | full adder has three inputs                              | ~           | (C)   | Boolean Expressions               |

| (C)        | Half adder has two inputs while                          |             |       |                                   |

|            | full adder has two outputs                               |             | (B)   | Minterm                           |

| (B)        | Half adder has one output while                          |             | (A)   | SOP                               |

|            | full adder has four inputs                               |             | •     | _                                 |

| (A)        | Half adder has two inputs while                          |             | repr  | esenting                          |

| and        | full adder is                                            | <b>33</b> . | Cano  | onical form is a unique way of    |

| 52. The    | difference between half adder                            |             | . ,   |                                   |

|            | gives one output                                         |             | (D)   | Latches                           |

| (2)        | decodes several inputs and                               | -           | (C)   | K-maps                            |

| (D)        | It is a type of encoder which                            |             | (B)   | Terms                             |

| (C)        | into many output                                         |             |       | _                                 |

| (C)        | It takes one input and results                           |             | (A)   | Registers                         |

| (0)        | many signals into one                                    |             | in    |                                   |

| (B)        | gives one output  It is a device which converts          |             |       | •                                 |

|            |                                                          |             | for : | simplifying Boolean expressions   |

| <u>(A)</u> | It is a type of decoder which decodes several inputs and | 54.         | Don   | 't care conditions can be used    |

|            | at is a multiplexer?                                     | _           | (0)   | The inputs and the outputs        |

|            | Odd parity to even parity                                |             | (D)   | Three inputs and two outputs      |

| •          | Single input, multiple outputs                           |             | (C)   | Two inputs and two outputs        |

| , ,        | AC to DC                                                 |             | (B)   | Three inputs and three outputs    |

| (A)        | Decimal-to-hexadecimal                                   |             |       |                                   |

| typ        | e of cinversion?                                         |             | (A)   | Two inputs and one output         |

| 50. Mos    | st demultiplexers facilitate which                       | 53.         | A fu  | ill adder logic circuit will have |

| 56. How many AND gates are required      | 59. How many select lines would be        |

|------------------------------------------|-------------------------------------------|

| to realize Y= CD+EF+G?                   | required for an 8-line-to-1-line          |

| (A) 1                                    | multiplexer?                              |

| J(B) 2                                   | (A) 3                                     |

| (C) 4                                    | <b>(B)</b> 2                              |

| LD) 3                                    | (C) 4                                     |

| 57. The gate which is called an inverter | (D) 8                                     |

| is called :                              | 60. In a full adder, the XOR gate is used |

| (A) NOR                                  | to calculate the:                         |

| (B) NAND                                 | (A) Carry output                          |

| (C) EXOR                                 | (B) Sum output                            |

| پې NOT                                   | (C) Both Sum and Carry                    |

|                                          | (D) None of the above                     |

| 58. D flip-flop is used as :             | 61. Hamming code is used for              |

| (A) Differentiator                       | (A) Error detection                       |

| (B) Delay switch                         | (B) Error correction                      |

| (C) Divider circuit                      | (C) None                                  |

| JD) All of these                         | (D) Both (A) and (B)                      |

| 2038\D\2024 [ 1                          | 12]                                       |

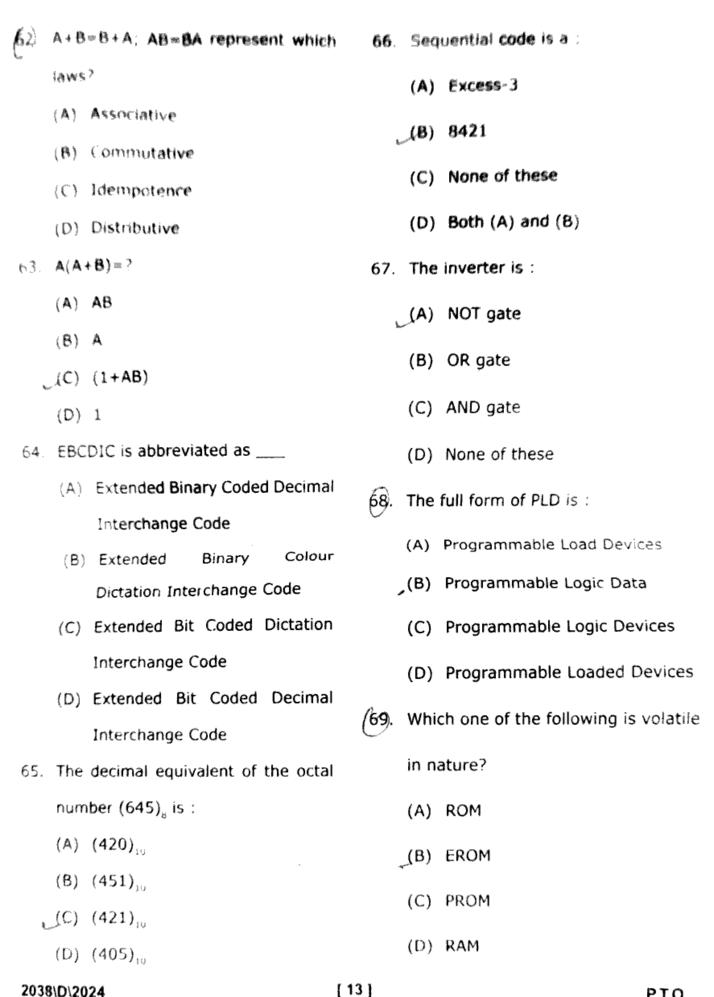

- 70. Excess-3 code is known as:

- (A) Weighted code

- (B) Cyclic rebundancy code

- (C) Self-complementing code

- (D) Algebraic code

- 11 Karnaugh diagram is used to:

- Prepare layout of a complicated circuit

- (B) Facilitate addition and multiplication in a computer circuit

- (C) Construct truth table

- (D) Reduce a digital logic circuit

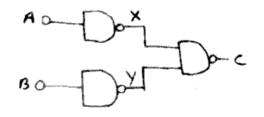

- 1. The circuit shown in figure is

functionally equivalent to:

- (A) AND gate

- (B) NOR gate

- (C) OR gate

- (D) EX-OR gate

2038\D\2024

- 73. The universal gate is:

- (A) NAND gate

- (B) OR gate

- (C) AND gate

- (D) None of the above

- 74. The binary number 10101 is equivalent to decimal number \_\_\_\_\_

- (A) 19

- (B) 12

- (C) 27

- (D) 21

- (75). Which of the following gate is a two-level logic gate :

- (A) OR gate

- (B) NAND gate

- (C) EXCLUSIVE OR gate

- (D) None of above

[14]